部落格

先進封裝發展趨勢

呂妙玲

先進封裝不僅可以最大化封裝結構I/O及晶片I/O,同時使晶片尺寸最小化,實現終端產品降低功耗並達到輕薄短小的目標。

日月光研發中心副總經理洪志斌博士說明,根據不同的應用需求,可選擇最適合的封裝技術,而不同的封裝技術都有其獨特的定位與特性,其中最典型的先進封裝技術包括晶圓級SiP封裝(Wafer level SiP)、扇出型封裝(Fan Out Packaging)、2.5D/3D IC封裝以及小晶片(Chiplet)技術。

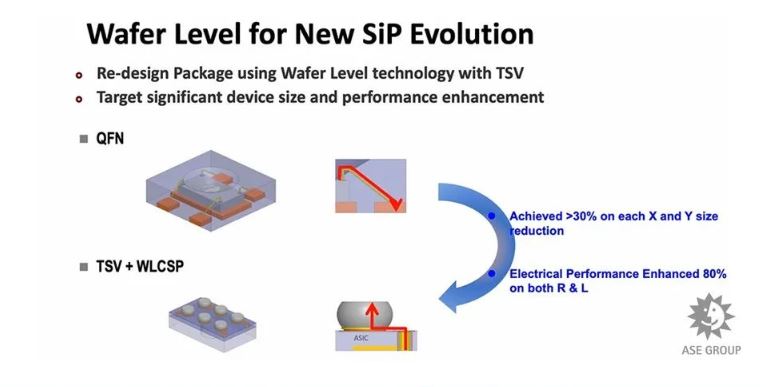

晶圓級SiP封裝可將常見的方形扁平無外引腳封裝(QFN),轉換成尺寸更小、有矽穿孔(TSV)的晶片尺寸級封裝(CSP) ,不僅減少30%的XY面積尺寸,同時減少80%的電阻,從而增強封裝結構的電氣效能。

扇出型封裝(Fan Out Packaging)具有靈活的RDL設計、更細的RDL線寬和空間、大約減少3層基底層等特性,不僅可調整系統性能,更可實現約高5倍的性能控制。因此更高頻率的應用、更好的性能和成本效益的扇出型封裝Fan Out適用于智慧手機、邊緣計算和物聯網(IoT)等領域。

2.5D/3D IC封裝具有集成GPU、CPU和記憶體以及被動元件(例如去耦電容)的優勢,具有超高佈線密度、超高I/O密度和I/O間距可擴展性等特性,以具有矽通孔(TSV)的矽中介層(Si Interposer)作為平臺,彌合封裝基板和半導體IC之間的I/O細間距能力差距,同時有助於保持焊盤間距(Pad to Pad clearance)縮放路徑而不受封裝基板技術的限制,可用于高端GPU、移動AP、大資料中心與5G基礎設施的路由器、人工智慧加速器等領域。

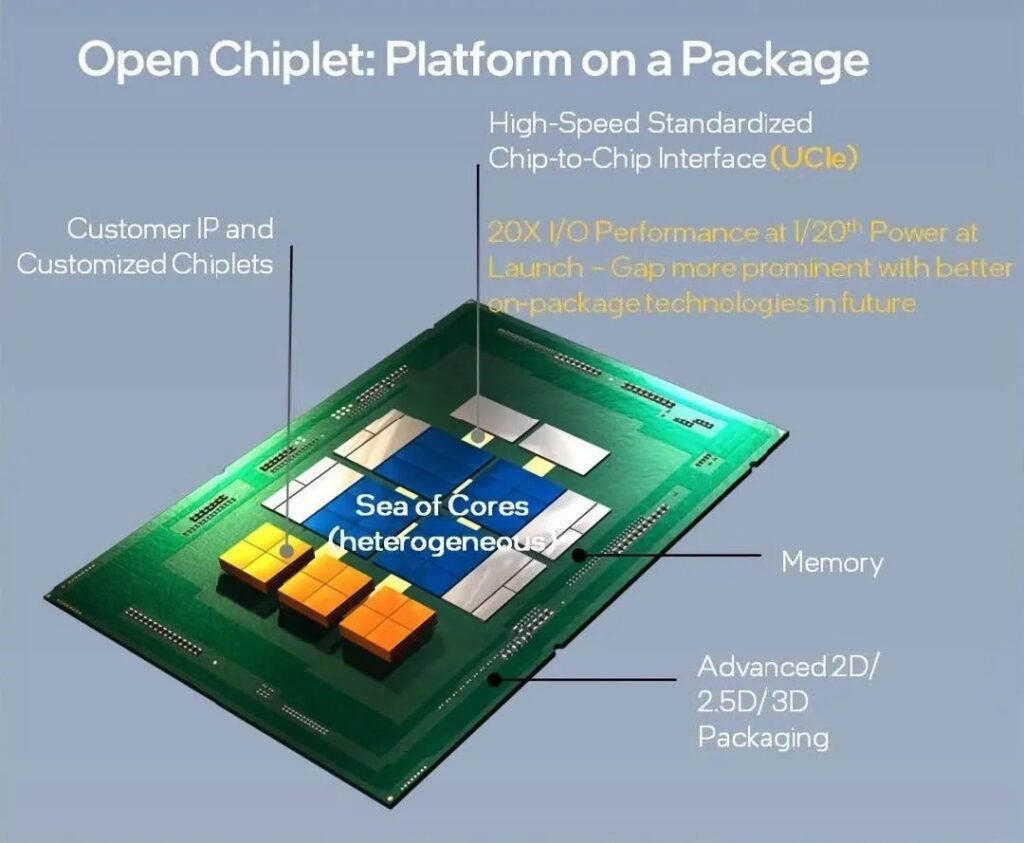

Chiplet技術將原有的大晶片拆分成多顆體積更小、產量更高、不同功能的小晶片,經過再設計和再製造,最終通過系統級封裝SiP異質整合成系統晶片,不僅不會增加原有晶片的面積,同時減少產品開發的時間成本及上市時程。

近日,日月光與AMD、Arm、Google Cloud、Intel、Meta、微軟(Microsoft)、高通(Qualcomm)、三星(Samsung)和台積電(TSMC)等半導體業者共同組成UCIe (Universal Chiplet Interconnect Express) 產業聯盟,推動晶片互連(die-to-die interconnect)技術標準化和促進開放式Chiplet生態系統。日月光在封裝和互連平臺技術的專業知識,有助於確保UCIe提出的標準切實可行,並且在封裝製造具有商業可行性和成本效益。

為確保封裝順利完成,不同的封裝技術需要掌握好異質的機械性質,真正實現針對不同用途需求的系統級封裝SiP集成,達到“晶片+封裝+系統”的整合綜效。日月光持續研發先進制程技術,洞悉市場趨勢,協助客戶減少晶片設計時程並加快產品開發速度。