部落格

異質整合先進封裝設計趨勢

洪志斌博士‒日月光研發中心副總經理

在半導體前段製程微縮日趨減緩後,異質整合先進封裝技術已然成為另一個實現功能整合與元件尺寸微縮的重要技術發展潮流。伴隨著人工智慧物聯網 (AI-centric IoT)、5G通信、高效能運算(HPC)和智慧汽車等主要半導體應用不斷發展,新興應用場域 (如生成式AI) 對於晶片封裝互連線的高密度、高速和低延遲需求與日俱增,推動異質整合先進封裝技術的需求不斷增長與突破。通過先進封裝技術實現異質整合,可在單一封裝內實現不同設計和製程節點的小晶片 (Chiplets) 整合,讓企業能依照需求選擇不同單價的製程,例如運算晶片採用3奈米、射頻晶片用7奈米,又或者快速產出特定功能的超級晶片,兼顧成本效益。除了追求更高的互聯密度外,異質整合還有一個重點,亦即把實現整個系統所需的各種元件 (如邏輯晶片、感測器、記憶體等) 都整合在單一封裝,使得能耗、效能獲得改善和大幅縮小體積。

推動AI高效能運算的先進封裝解決方案

目前用於AI雲端運算處理器的高密度先進封裝,其尺寸至少都是55mm x 55mm以上,其封裝基板上的佈線層一般至少是5-2-5 (上面5層、中間2層、下面5層),甚至可多達11-2-11。其封裝型態一般是使用扇出型技術加上silicon bridge,也可以是2.5D封裝,以矽中介層 (Si Interposer) 作為小晶片的整合平台。業界的目標都是在同樣的空間中,獲得更多算力。

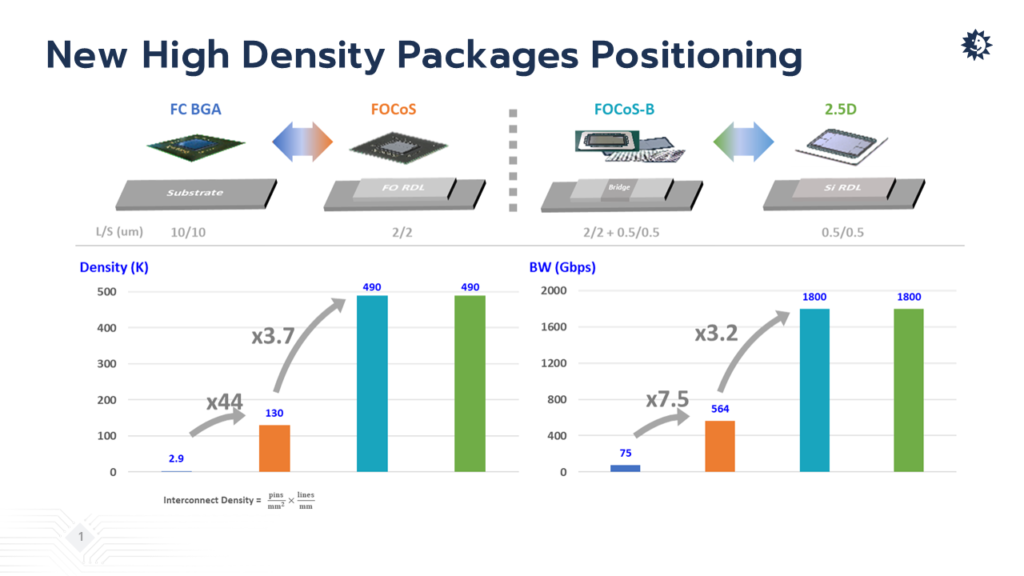

日月光提供的高密度封裝的解決方案:包含覆晶球格陣列封裝 (FCBGA)、Fan Out Chip-on-Substrate (FOCoS)、FOCoS-Bridge以及2.5D封裝等三大類。FCBGA晶片間封裝互連線的整合是透過BGA基板達成,其最小L/S (線寬/線距) 一般僅能達到10μm/10μm。目前很熱門、供不應求的CoWoS (Chip on Wafer on Substrate) 是一種2.5D封裝技術,以矽中介層 (Si Interposer) 上的重佈線層 (RDL) 連接整合小晶片,可以將L/S大幅微縮到0.5μm/0.5μm。由於矽中介層需要承載所有的晶片 (以相肩比鄰的方式排列),因此面積越來越大,使得每片12吋晶圓能切割出的矽中介層晶片越來越少 (一般少於五十顆),導致2.5D封裝的製造成本也隨之大幅上升。但是並非所有應用皆需要0.5μm/0.5μm的L/S,因此日月光發展FOCoS (Fan Out Chip-on-Substrate),利用扇出型技術的RDL來整合不同小晶片,其L/S可以達到2μm/2μm,其優勢是以相對較低的製造成本,提供市場不同的解決方案。此外ASE的FOCoS-Bridge技術利用高密度連接線矽橋 (silicon bridge),L/S可以達到0.5μm/0.5μm,在需要高速傳輸的區域連接不同晶片 (例如邏輯晶片和記憶體),而在其它區域以Fan-Out RDL整合,因此在L/S設計上可以兼具0.5μm/0.5μm + 2μm/2μm的彈性,同時達成封裝密度以及頻寬的大幅提升。

高效能晶片/封裝/系統共同設計(Co-Design)

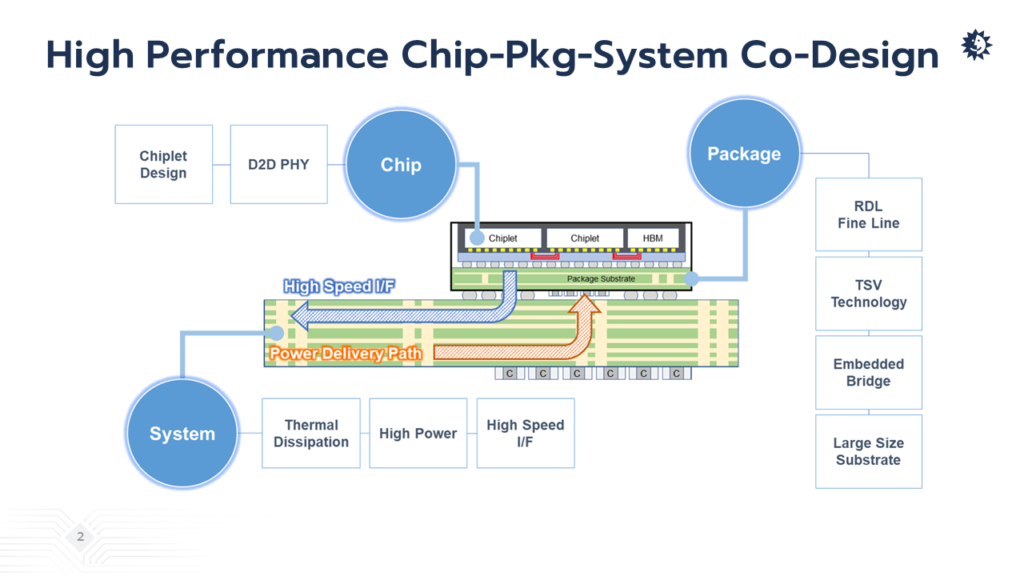

要達成前述的頻寬大幅提升,需要由晶片、封裝一直到整個系統都要一起考慮,以實現整個系統而不僅是個別元件的Holistic Design最佳化。利用電子設計自動化 (EDA) 作設計最佳化的時候,需要考量訊號在整個傳輸路徑上會有多少改變,例如需考量Cu pillar, RDL fine line, TSV, μbump等,最後利用眼圖 (eye diagram) 分析 SerDes electrical performance。針對高速訊號差動對線 (differential pairs) 設計的時候,需要降低反射損耗 (return loss) 及插入損耗 (insertion loss),尤其是在工作的頻段。台灣的優勢在於我們能夠做到由晶片、封裝到整個系統,從頭到尾的完整設計。

如何節省Power達到更大的每瓦算力

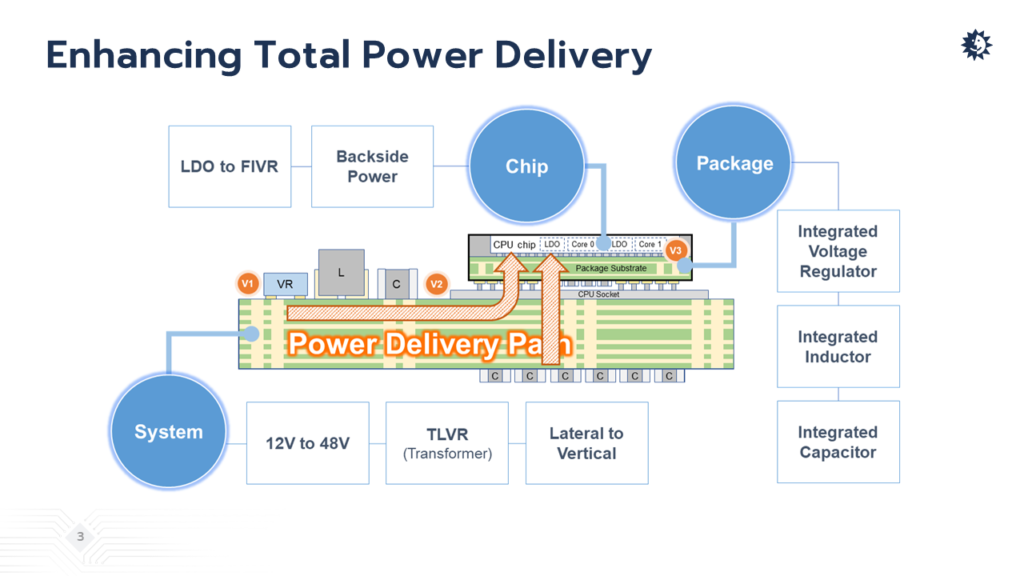

目前業界都在思考一件事情,本來放在系統上的Power元件,能不能放在離Package或Processor晶片越近越好;甚至重新思考設計供電架構,例如直接由晶片背面供電 (Chip Backside Power Delivery)。

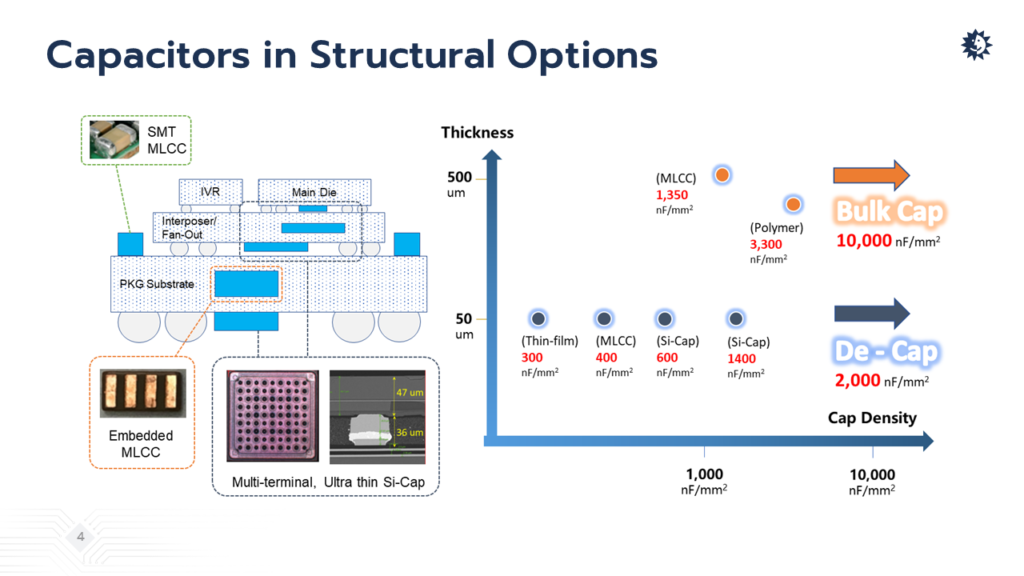

供電網路(PDN)電源完整性設計

電容放對位置可以有效增進電源完整性 (Power integrity),降低電源雜訊 (Power Noise),雖然理論上電容離晶片越近越好,但是需要考量電容的尺寸以及製程,讓整體最便宜,效果最好。常見的SMT電容都是蠻大一顆,但現在已經有晶片層級的矽電容 (Si-Cap),也都可以提供不錯的電容值。

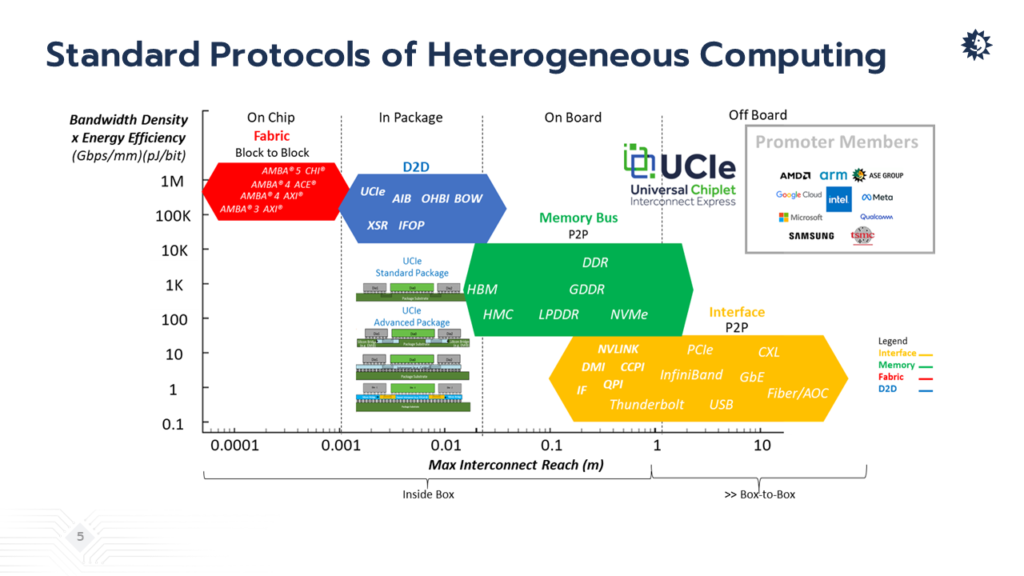

UCIe (Universal Chiplet Interconnect Express) 產業聯盟

傳統進行系統設計的時候,在晶片端、系統板 (System Board)上,可以看到許多標準通信協定 (例如Memory Bus、Interconnection interface Protocol),封裝雖也有一些協定,但是大家沒意識到這麼重要。直到最近2.5D、FOCoS封裝技術在針對小晶片設計中所面臨的挑戰中,業界發現需要有一個共通的Universal Interface;2022年3月Intel邀請半導體產業鏈上下游廠商共組UCIe產業聯盟,將小晶片資料傳輸架構標準化,以降低先進封裝設計成本。日月光很榮幸成為創始會員 (Promoter member),我們擁有最多的先進封裝型態,把這些封裝設計規範融合進來後,可以連結晶圓代工廠的解決方案,以及系統原始設備製造商 (OEM) 及雲端服務提供者的系統需求;需求整合後,新的UCIe Package Standard就可以佈建出來,協助各種不同先進封裝技術架構 (如2.5D、3D、FOCoS、Fan-out、EMIB、CoWoS等),在未來高階運算半導體封裝,實現無處不在的小晶片異質整合互連。這也表示台灣開始可以在標準的制定方面扮演角色,為業界提供整合的解決方案。

異質整合的概念已經發展多年,不只可以用在異質小晶片間的整合,也可以把其他非晶片的主/被動元件,甚至連接器都整合在單一封裝體內。要做到這點,不只需要封裝技術,更需要設計跟測試的配合。日月光可以提供從設計、封裝到測試的一條龍服務方案,協助客戶減少晶片設計時程並加快產品開發速度。