嵌入式基板

With the anticipated market needs of integrating more chips and functions, higher performance, lower power consumption and better heat dissipation onto a smaller form factor, demand for embedded die substrates, such as a-EASI or SESUB, is expected to increase globally.

ASE offers customers a full turnkey solution of embedded die substrates through our advanced packaging and test expertise as well as substrate design and manufacturing capability.

What is Embedded Die Substrate?

Conventionally, active semiconductor chips (or dies) are mounted on top of a substrate for structural support and electrical interconnect. But in the embedded die substrate, a semiconductor die is embedded within standard PCB material (i.e., a plurality of organic laminated layers) and/or a lead frame during formation of the substrate. The semiconductor die is then electrically connected to other components (MEMS or passives) on/in the substrate through copper-plated vias and conductive traces of the substrate.

Advantages of Embedded Die Packaging

Miniaturization & Design Flexibility

- Embedded chip enables more space for other components or shrinks overall solution

- Design flexibility now shifts from 2D to 3D

Improved Thermal & Electrical Thermal Performance

- Shorter interconnections reduce parasitics - minimizes distortion and power loss

- Lower electrical & thermal resistivity in package improves power performance

Improved Reliability and Mechanical Stability

- High mechanical system stability due to stable Cu interconnections

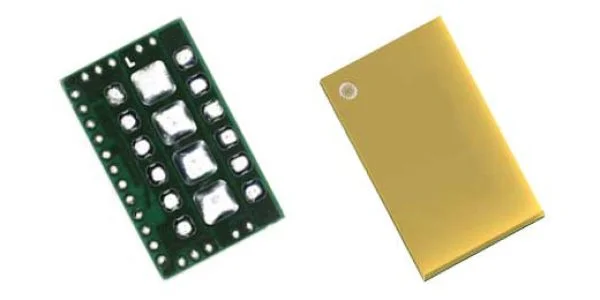

ASE's Embedded (Chip) Technology is considered an alternative solution to achieve higher-level integration with multi-functionalities and form factor shrinkage advantages. ASE a-EASI is suitable for power electronics applications to reduce power loss and high thermal dissipation which also had robust mechanism. Embedded Technology provides SMT integration and flexible routing solution to reduce PCB size. The short connection path though Cu via structure. a-EASI applied metal lead frame to die placement which has high thermal dissipation and EMI benefit.

Applications

- MOSFET

- IGBT

- Regulator

- Power modules

- DCDC

Features

- Pinout: BGA/LGA/QFN

- IOs: Up to 100

- Package size: <50 (mm²)

- Power: 1000+ (W)

- Thermal: Excellent

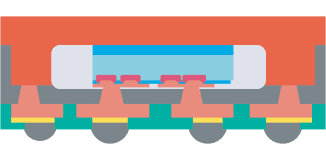

P1 Structure

via direct on chip pad

- Excellent electrical & thermal performance

- HVM production proven

P2 Structure

- Thermal enhance (exposed pad)

- Thinner package

- Support various footprint (BGA, LGA, QFN)

- Single die pass AEC-Q100 G1 by customer

- Embedded 8 chips max. (under customer qualification)

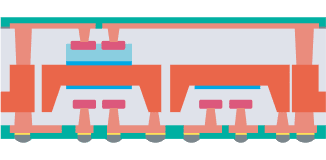

P3 Structure

via direct on chip pad

- Improve design flexibility for vertical current device

- Highly integration – smaller form factor

SESUB (Semiconductor Embedded in SUBstrate) is a technology that embeds the IC in the laminated substrate. This substrate with the thinned IC embedded can be mounted with various electronic components to form a highly integrated, multiple-function module/package. SESUB enables the micro-modularization of functional circuitry such as high-performance PMUs for smartphones as well as Bluetooth modules. SESUB has already been a proven technology by many customers and IC vendors.

Applications

A broad application coverage including:

- MCU

- FEM

- PMIC

- Optical

- Connectivity

- Audio

- Power

- Sensor

- Processor

- Image module

- Automotive ADAS

- High-Frequency Application

- Memory

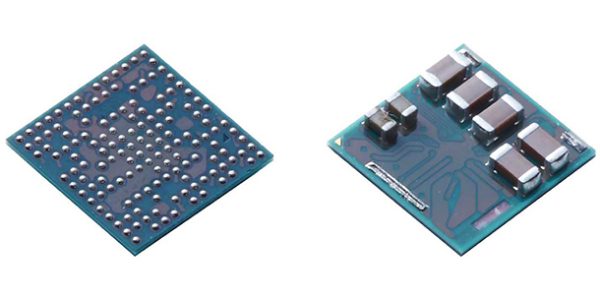

Features

- Pinout: BGA/LGA

- IOs: Up to 1000

- Package size: 200+ (mm²)

- Power: <20+ (W)

- Thermal: Good

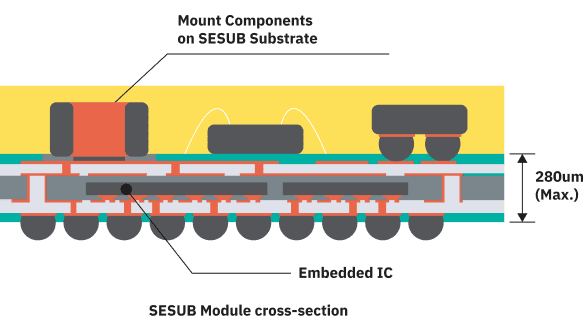

The figure below illustrates the cross-section view of a multi die embedded module utilizing SESUB technology. The SESUB is a 1-2-1 4-layer structure which provides properties for size reduction, thermal dissipation, mechanical robustness, performance improvement. SESUB not only serves as module, but also as package with thin thickness.

The properties include

- Multi-die embedded in substrate

- Thin substrate thickness max. 280um

- Small form factor

- Low profile

- Enhance heat dissipation

- Mitigate unwanted noise radiation

- JEDEC MSL3 certified

- Very thin die thickness min. 50um

- High integration package

- Space saving

- Low noise emission

- Robust copper connection

- SMT on surface of substrate