post

異質整合加速人工智慧(AI)經濟

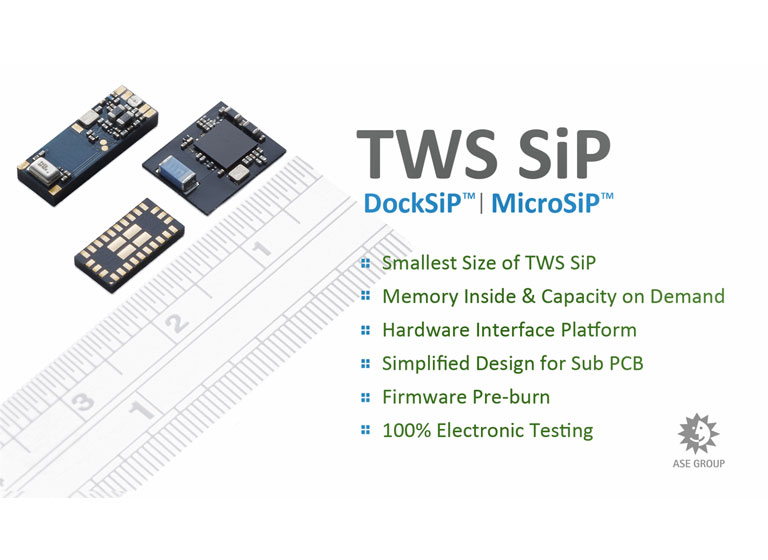

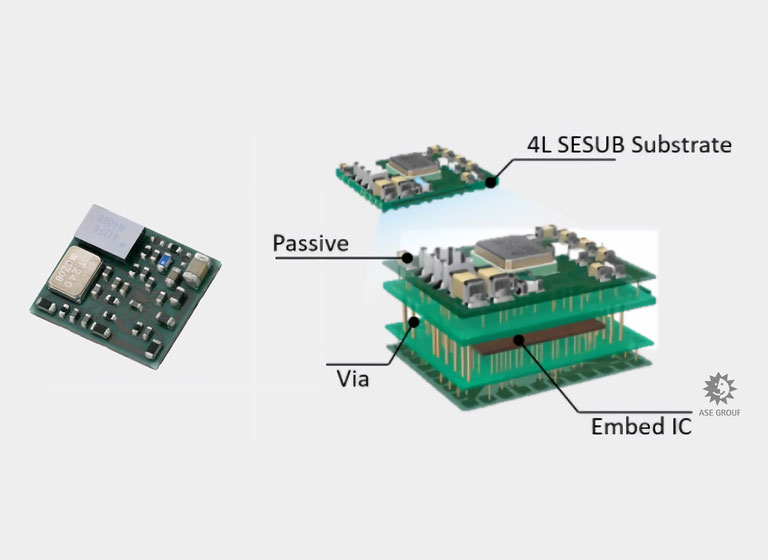

世界正迅速從網際網路經濟轉向人工智慧經濟。在網際網路時代,我們透過手機、個人電腦和物聯網設備,一天24小時每天不斷地保持網路連線。然而,在AI時代,我們所做的一切都將與人工智慧相關聯。您可能已經聽說過像 ChatGPT 或 Google Gemini 這樣的AI工具,它們可以回答問題並創建非常類人的(human-like)文字、圖像、甚至影片。未來,多模態人工智慧(multimodal AI)甚至可以模仿人類的生物感官,使其能夠看見、聽到,甚至是嗅到您所需的事物。此外,主動式人工智慧(agentic AI)將能夠理解其環境,自主設定目標,並且在幾乎沒有直接人為監督的情況下,採取行動以實現這些目標。這僅僅是人工智慧對我們生活帶來變革的幾個例子。然而,要實現AI變革需要更多的創新和更先進的半導體以及封裝解決方案。 人工智慧帶來哪些影響? 回顧歷史上科技驅動的成長機會,我們可以看到每個科技轉折點都增加了對半導體的需求。50 年前,航太產業僅需要數千個,但隨著手機需求的劇增,這個數字已經增加到 20 億,而智慧物聯網更需要高達 100 億。 我們相信,AI將在短時間內將需求增加三倍到 300 億。因為我們預期PMMP(People-Machine-Machine-People)通訊模式將成為新的常態,每個人的手機將運行各式各樣的AI應用程序,藉由連通多個雲端伺服器,提供大家所需的訊息和功能。這些機器與機器之間的相互協作將大幅增加,推動半導體產值衝破1兆美元。 邁向AI時代:透過異質整合克服挑戰 進入人工智慧時代,規模擴展(scaling)面臨許多重大挑戰。過去兩年(2021 ~ 2022),對於AI/ML 效能的市場需求增加了將近 6.8 倍至 11 倍,遠超出摩爾定律電晶體數量每 18 個月翻倍的增率。 能耗是另一個挑戰,在未來十年內,AI產業將建置達千兆位元(zettabyte)級別的數據中心,需要 500 兆瓦(MW)的電力驅動,約相當於半個核電廠的輸出。長遠來說,這是相當不永續的,我們需要找到更節能的方式來滿足人工智慧經濟所需的算力(Computing Power)。 成本也是需要考量的重點,儘管半導體製程新節點的導入速度正在減緩,但生產成本仍在不斷增加。5 奈米(5 nm)先進 IC 設計的開發成本可能高達 5 億美元,大部分的人都無法負擔。 我們需要尋找新的效率,日月光認為異質整合是關鍵,它提供了一種可減少能耗、超越「摩爾定律」,並降低整體開發成本的方法。 用於AI高效能運算的異質整合先進封裝 日月光先進封裝技術可以將個別製造的各種元件整合到小晶片(Chiplets)、系統級封裝(SiP) 或模組中,即使這些元件的材料、製程節點和製造技術完全不同。異質整合不僅可以增加功能密度,降低每個功能的成本,還為系統架構師提供了設計靈活性,用以創建增強 系統性能和效率的創新解決方案,滿足人工智慧和高效能運算的需求。 我們的次世代 3D 異質整合架構 VIPack™ 設計旨在擴展設計規則,實現以下目標:… Read More