部落格

Thermal and Mechanical Characterization of 2.5D and Fan-Out Chip on Substrate Chip-First and Chip-Last Packages

Meng-Kai Shih; Weihong Lai; Tsewei Liao; Karen Chen; Dao-Long Chen; C. P. Hung

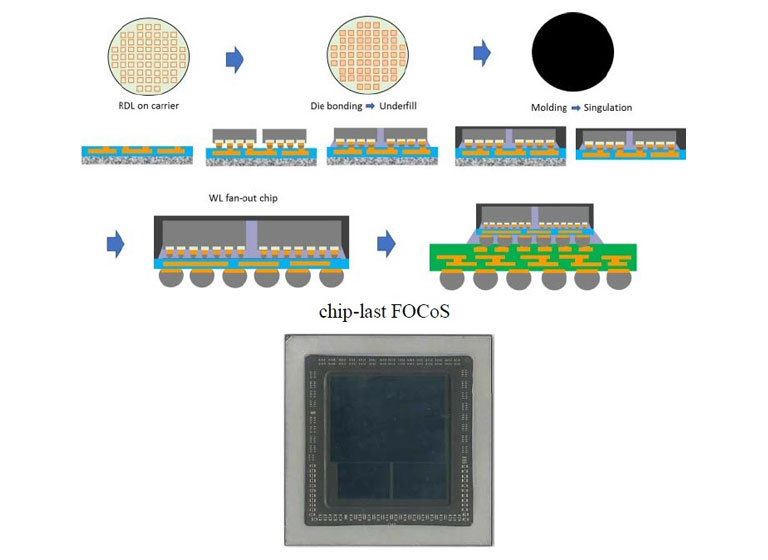

Heterogeneous integration technology makes possible the integration of multiple separately manufactured components into a single higher level assembly with enhanced functionality and improved operating characteristics. Various types of advanced heterogeneous packages are available, including 2.5-D integrated circuit (IC), fan-out chip on substrate (FOCoS) chip-first, and FOCoS chip-last. This study constructs a nonlinear simulation technique (3-D simulation model) to explore the warpage, extreme low- k (ELK) interconnect stress, redistribution layer (RDL) trace stress, and board-level solder joint reliability of all three packages. The validity of the simulation model is confirmed by comparing the numerical results for the in-plane dimensional change of an FOCoS chip-last package with the experimental observations over the temperature range of 30 °C–260 °C. The thermal performance (i.e., junction-to-ambient thermal resistance) of the three packages is then examined and compared. Finally, 25 factorial designs with the analysis of variance (ANOVA) are conducted to examine the effects of the main structural design parameters of the FOCoS chip-last package on its thermomechanical reliability under typical thermal loading conditions. It is shown that a thinner polyimide (PI) layer is beneficial in improving the package reliability by minimizing the coefficient of temperature expansion (CTE) mismatch between the PI layer and the RDL trace, respectively.

Published in: IEEE Transactions on Components, Packaging and Manufacturing Technology ( Volume: 12, Issue: 2, February 2022)