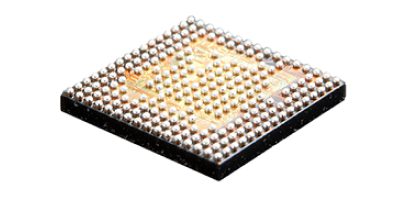

Wafer Level Package

ASE is with solid experience and superior capability to provide a broad range of Wafer Level Package (WLP) solutions from chip scale packages to SiP to homogeneous and heterogeneous chip integration. ASE is able to provide thinnest profile, lower-power consumption and high-performance solutions.

ASE WLP solution meets current needs in various applications from client device to infrastructure and high-performance cloud computing, even emerging appliance such as VR/AR, autonomous driving, smart Robots.

ASE Wafer Level Packaging Offerings

To service the fast-growing market within PDA and cell phone, this smaller chip size is essential. In 2001, ASE licensed Ultra CSP® from Kulicke & Soffa's Flip Chip Division. ASE also provided several enhanced structures called "aCSP™" by polyimide, PBO, or thicker Cu RDL to meet various customer demands. aCSP™ is a wafer level CSP package that can be Direct Chip Attached to the PCB board without any interposer. Also, aCSP™ provides the shortest electrical path from Al pad to PCB board to enhance the electrical performance. It has been broadly used in portable devices in passives, analog and logic applications, and is extending to RF applications.

Applications

- Bluetooth/Wi-Fi

- Analog Devices

- Power and Voltage Regulator

- Cell Phones and System Boards

- GPS

- Microcontrollers/Integrated Passives

- Power Amplifier

- FM Radio

- EEPROM

- RF Devices

Features

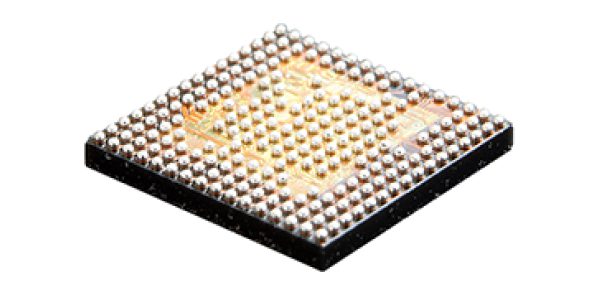

- Real chip size (smallest, thinnest and lightest)

- High-density interconnection

- High-speed data processing

- Batch process-assembly processed in wafer form

- Wire-bond type die can be directly switched to Acsp

Product Offerings

- aCSP: Through ball drop process

- WLCSP: Through ball printing/plating process

Advanced Technology under Development

- Wafer technology: Qualification for 22 and 16nm wafer

- Ball pitch: 300um

- Ball size: 150um ball drop

- Grinding: Die thickness 150um

- Plated RDL line/width: 10/10um; 8/8um

- Plated RDL thickness: >=7um

- Sawing: Laser sawing

aWLP has higher I/O than wafer level package. It is a substrate-less solution with small form factor, improved electrical and thermal performance. aWLP is a die down fan out wafer level package with molding compound surrounded, ideally designed for communication devices with constrained space.

Applications

- Baseband

- RF

- Codec

- PMICs

- Car Radar

Features

- Improved electrical and thermal performance

- Die down FOWLP with molding compound surrounded

- Single die package & 2 dies (side-by-side) embedded structure approached

- Finer line width/space = 2/4um

- 3 layers RDLs approached (min.)

- Support package size up to 10 x 10mm (max.)

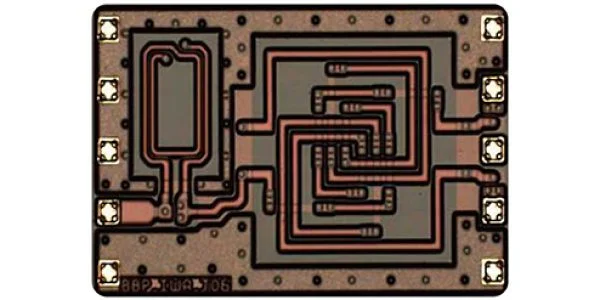

ASE Wafer Level Integrated Passive Device (WL IPD) is a glass-based wafer level process, well developed for today's most advanced RF communication solutions. It is with custom design, high-performance and small form factor, fully compatible with current assembly process in QFN, BGA/LGA, Flip Chip packages, and in WLCSP. AIC (above IC) process is also available.

Applications

Most of current applications are in the RF solutions, specific functional devices, such as resonator, filter, diplexer, balum, transformer, etc. ASE IPD is a custom design solution, any other opportunities for IPD is welcomed.

Features

- High-accuracy 200mm thin film process

- Very low-loss glass substrate

- High Q-factor inductor: 10 or 15um Cu

- Single or double layer

- Integrated package and turnkey solutions