post

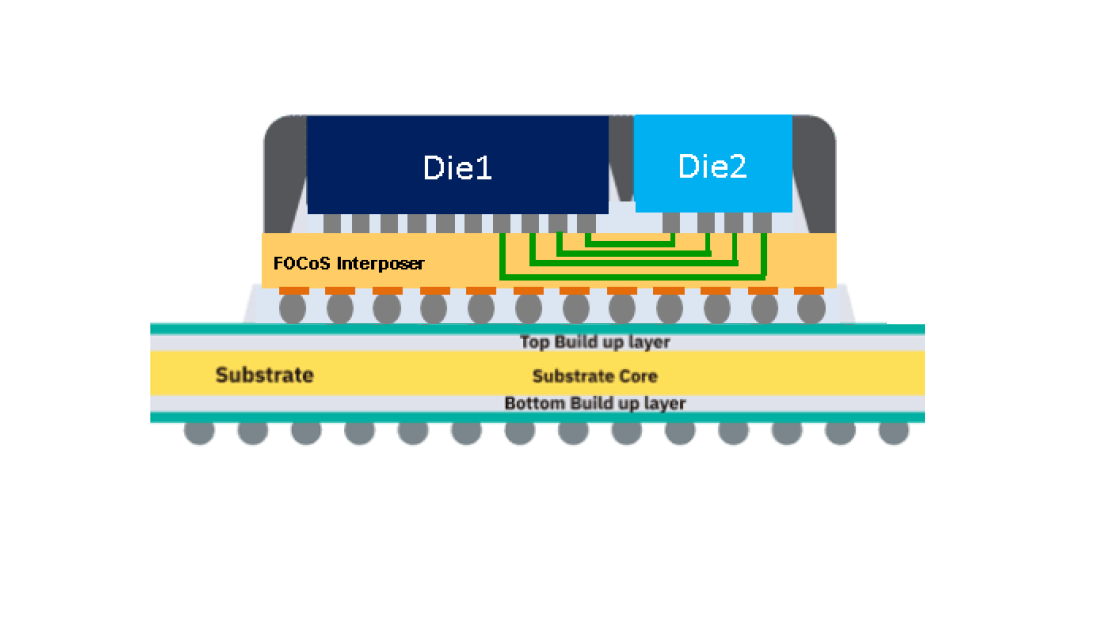

Integrated Design Ecosystem™ for Chiplets and Heterogeneous Integration in Advanced Packaging Technology

As the demand for high-performance computing (HPC) continues to grow, chiplets and heterogeneous integration have emerged as key solutions due to their significant advantages in improving yield, reusing IP, enhancing performance, and optimizing costs. The integration of chiplets, particularly for AI applications, necessitates a greater number of connections than traditional… Read More