Blog

Heterogeneous Integration Fuels the Future

Patricia MacLeod

Moore’s Law has driven the semiconductor industry for decades, but in recent years, there has been deceleration in terms of performance and economic benefit. The exponential cost of silicon scaling has created an inflection point for the industry, and that is driving the development of More-Than-Moore technologies to augment device functionality and strengthen system performance.

A Brief History of Semiconductor Roadmaps

The semiconductor industry comprises highly specialized yet closely interdependent companies that must stay on top of technology and market application trends to keep developments on track. As the industry grew, it became imperative by the 1990s that global semiconductor companies must work together to ensure progress was heading in the same direction.

In 1991, semiconductor companies in the United States, under the auspices of the Semiconductor Industry Association (SIA), first established the National Technology Roadmap for Semiconductors or NTRS. By 1998, roadmapping efforts had expanded when companies from Japan, Europe, Korea, and Taiwan joined the NTRS effort, and together with SIA, they formed the International Technology Roadmap for Semiconductors (ITRS). SIA brought ITRS to a close in 2015, and that is when the Heterogeneous Integration Roadmap, or HIR, was initiated.

Heterogeneous Integration Will Take Us Forward

Heterogeneous Integration refers to the integration of separately manufactured components into a higher-level assembly system-in-package (SiP) that in the aggregate provides enhanced functionality and improved operational characteristics. It is now the key technology direction going forward, driving the pace of advancement for greater intelligence and connectivity, higher bandwidth and performance, and lower latency and power per function, all at a more manageable cost.

The Heterogeneous Integration Roadmap (HIR) is a roadmap to the future of electronics that identifies technology requirements and potential solutions. The primary objective is to stimulate pre-competitive collaboration among industry, academia, and government to accelerate progress. HIR is designed to provide long term continuity and a broad technology base. It is organized with sponsorship by three IEEE Technical Societies (Electronics Packaging Society, Electron Devices Society, and Photonics Society) together with SEMI and ASME Electronics and Photonics Packaging Division (EPPD). Technology takes a long time to develop and mature, and increasingly involves the collective knowledge from overlapping fields. It is therefore essential to set goals for the long-run and cover as many subjects and fields as possible, related to heterogeneous integration.

As the industry enters the digital transformation and exascale computing era, massive compute with frequent access to data is required for high performance computing (HPC) applications. The increasing amount of data from all sectors is raising the issue of operational and storing cost of the data. The advent of artificial intelligence (AI) and machine learning (ML) requires large amounts of data to be processed and is driving an entirely new computing paradigm from edge computing to cloud to data centers.

Traditional IC design trends are to pack more transistors on a monolithic die or system-on-chip (SoC) at each process node, resulting in difficult chip scaling for the integration of analog, logic, and memory circuits. The heterogeneous integration approach is die-partitioning or chiplets, which offers a compelling value proposition for yield improvement, IP reuse, performance, and cost optimization, as well as time-to-market reduction.

Chiplet integration has the potential to allow the integration of disparate technologies from multiple suppliers to provide more flexible mix-and-match systems to accelerate performance and improve power efficiency without requiring the deployment of these technologies across an entire SoC simultaneously. Chiplet solutions start with internal designs within a system integrator. However, as IP interface standards are developed, the commercialization of chiplets in the market will proliferate. Heterogeneous Integration through chiplets will play a critical role for future HPC and AI/ML applications.

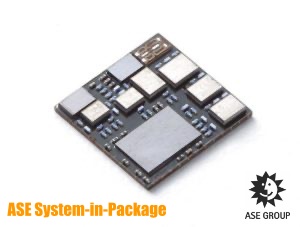

ASE System-in-Package (SiP) Demonstrates Heterogeneous Integration.

ASE has developed and offers a wide portfolio of Si-level integration technology solutions, from low- to high-density chiplet integration including flip-chip multi-chip-module (FC-MCM), fanout chip-on-substrate (FOCoS), and 3D IC. The advanced FOCoS technology can provide short die-to-die connection and high interconnections (10,000s), redistribution layers (RDL) with 2µm line/space, and up to four layers for chip-first and chip-last packaging processes. It produces a lower-cost solution with improved electrical performance compared to a 2.5D Si interposer solution due to the elimination of Si through silicon via (TSV) processes and reduced insertion loss. ASE is evolving this advanced packaging platform to meet application demands for HPC and AI/ML applications.

As a leading semiconductor packaging, test, and system service provider, ASE has heavily invested in both chip-level (SoC) package integration and system-level integration. The development of cutting-edge heterogeneous integration technologies addresses functional areas from silicon integration, power integration, optical integration to system integration that form the backbone of many electronic components, subsystems, and electronics products.

A Smarter, Healthier, More Efficient Future

Looking further into 2021 and beyond, key developments in packaging that create higher performance systems and utilize less power will be deployed. System performance will continue the pace of Moore’s Law era, albeit in a different way than with the previous total reliance on semiconductor chip lithography and SoC integration. There is tremendous optimism that innovations in the IC packaging industry will continue on a heterogeneous integration journey. Discovery, creativity, innovation, and very importantly, collaboration – will enable applications that make our world smarter, healthier, and infinitely more efficient.

This article has been adapted from the blog article ‘The Future is Heterogeneous Integration’ by Dr Bill Chen. To read the full article, please click on https://www.3dincites.com/2021/01/the-future-is-heterogeneous-integration/